Developer Note

# Epic Computer

Developer Note Seed Draft APPLE CONFIDENTIAL

8/26/96 Developer Press © Apple Computer, Inc. 1995, 1996 Apple Computer, Inc. © 1996 Apple Computer, Inc. All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, mechanical, electronic, photocopying, recording, or otherwise, without prior written permission of Apple Computer, Inc., except to make a backup copy of any documentation provided on CD-ROM. Printed in the United States of America.

The Apple logo is a trademark of Apple Computer, Inc. Use of the "keyboard" Apple logo (Option-Shift-K) for commercial purposes without the prior written consent of Apple may constitute trademark infringement and unfair competition in violation of federal and state laws.

No licenses, express or implied, are granted with respect to any of the technology described in this book. Apple retains all intellectual property rights associated with the technology described in this book. This book is intended to assist application developers to develop applications only for Apple-labeled or Apple-licensed computers.

Every effort has been made to ensure that the information in this manual is accurate. Apple is not responsible for printing or clerical errors.

Apple Computer, Inc. 1 Infinite Loop Cupertino, CA 95014 408-996-1010

Apple, the Apple logo, AppleLink, Apple SuperDrive, AppleTalk, LaserWriter, LocalTalk, MacTCP, Macintosh, PowerBook, and Power Macintosh are trademarks of Apple Computer, Inc., registered in the United States and other countries. Finder, Mac, and QuickDraw are trademarks of Apple Computer, Inc. Adobe, Adobe Photoshop, and PostScript are trademarks of Adobe Systems Incorporated, which may be registered in certain jurisdictions. DECnet is a trademark of Digitial Equipment Corporation. Helvetica and Palatino are registered trademarks of Linotype Company. ITC Zapf Dingbats is a registered trademark of International Typeface Corporation. NuBus is a trademark of Texas Instruments.

PowerPC is a trademark of International Business Machines Corporation, used under license therefrom.

SoftWindows is a trademark used under license by Insignia from Microsoft Corporation. UNIX is a registered trademark of

Novell, Inc. in the United States and other countries, licensed exclusively through X/Open Company, Ltd.

Simultaneously published in the United States and Canada.

# LIMITED WARRANTY ON MEDIA AND REPLACEMENT

If you discover physical defects in the manual or in the media on which a software product is distributed, ADC will replace the media or manual at no charge to you provided you return the item to be replaced with proof of purchase to ADC.

ALL IMPLIED WARRANTIES ON THIS MANUAL, INCLUDING IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE, ARE LIMITED IN DURATION TO NINETY (90) DAYS FROM THE DATE OF THE ORIGINAL RETAIL PURCHASE OF THIS PRODUCT.

Even though Apple has reviewed this manual, APPLE MAKES NO WARRANTY OR REPRESENTATION, EITHER EXPRESS OR IMPLIED, WITH RESPECT TO THIS MANUAL, ITS QUALITY, ACCURACY, MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE. AS A RESULT, THIS MANUAL IS SOLD "AS IS," AND YOU, THE PURCHASER, ARE ASSUMING THE ENTIRE RISK AS TO ITS QUALITY AND ACCURACY.

IN NO EVENT WILL APPLE BE LIABLE FOR DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES RESULTING FROM ANY DEFECT OR INACCURACY IN THIS MANUAL, even if advised of the possibility of such damages.

THE WARRANTY AND REMEDIES SET FORTH ABOVE ARE EXCLUSIVE AND IN LIEU OF ALL OTHERS, ORAL OR WRITTEN, EXPRESS OR IMPLIED. No Apple dealer, agent, or employee is authorized to make any modification, extension, or addition to this warranty.

Some states do not allow the exclusion or limitation of implied warranties or liability for incidental or consequential damages, so the above limitation or exclusion may not apply to you. This warranty gives you specific legal rights, and you may also have other rights which vary from state to state.

# Contents

Figures and Tables vii

# Preface About This Developer Note ix

Contents of This Note ix Supplemental Reference Documents x Apple Publications x Other Publications xi Conventions and Abbreviations xi Typographical Conventions xi Standard Abbreviations xii

1

## Chapter 1 Introduction

Features2New Features2Modified Features2Unchanged Features3Appearance4Configurations5Peripheral Devices6

Chapter 2

### Architecture 7

Devices on the Processor Bus 8 Main Processor 8 9 RAM 10 ROM PBX Memory Controller IC 10 Memory Control 10 **Bus Bridge** 10 Devices on the I/O Bus 10 Whitney Peripheral Support IC 11 Combo IC 12 Singer IC 12 12 Power Manager IC Display Controller IC 12 Video Card Connector 12 Baboon Custom IC 13 Floppy Disk Controller IC 13

### TREX Custom IC 13

| Chapter 3 | I/O Features 15                                 |  |  |  |  |

|-----------|-------------------------------------------------|--|--|--|--|

|           | Internal IDE Hard Disk Drive 16                 |  |  |  |  |

|           | Hard Disk Specifications 16                     |  |  |  |  |

|           | Hard Disk Connector 17<br>Signal Assignments 18 |  |  |  |  |

|           |                                                 |  |  |  |  |

|           | IDE Signal Descriptions 19                      |  |  |  |  |

|           | Trackpad 20                                     |  |  |  |  |

|           | Keyboard 20                                     |  |  |  |  |

|           | Flat Panel Display 22                           |  |  |  |  |

|           | Flat Panel Display Circuitry 22                 |  |  |  |  |

|           | Number of Colors 22                             |  |  |  |  |

|           | Serial Port 23                                  |  |  |  |  |

|           | SCSI Port 23                                    |  |  |  |  |

|           | ADB Port 24                                     |  |  |  |  |

|           | Infrared Link 25                                |  |  |  |  |

|           | Sound System 26                                 |  |  |  |  |

|           | Sound Inputs 26                                 |  |  |  |  |

|           | Sound Outputs 27                                |  |  |  |  |

|           |                                                 |  |  |  |  |

|           |                                                 |  |  |  |  |

Chapter 4

# Expansion Modules 29

| Expansion Bay 30                                            |

|-------------------------------------------------------------|

| Expansion Bay Module for Floppy Disk 30                     |

| Expansion Bay Module for CD-ROM 33                          |

| Expansion Bay Connectors 34                                 |

| Signals on the Floppy Disk Connector 34                     |

| Signals on the CD-ROM Connector 36                          |

| Unused Signals 39                                           |

| User Installation of an Expansion Bay Module 39             |

| Sequence of Control Signals 39                              |

| Guidelines for Developers 40                                |

| RAM Expansion Cards 40                                      |

| Electrical Design Guidelines for the RAM Expansion Cards 41 |

| Connector Pin Assignments 41                                |

| Signal Descriptions 43                                      |

| Address Multiplexing 44                                     |

| RAM Banks 46                                                |

| RAM Bank Selection 47                                       |

| DRAM Device Requirements 48                                 |

| RAM Expansion Card Electrical Limits 48                     |

|                                                             |

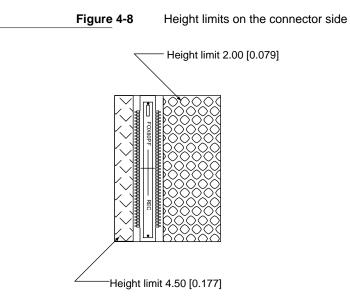

| Mechanical Design of the RAM Expansion Cards 49    |  |  |  |

|----------------------------------------------------|--|--|--|

| Design of the User-Installed RAM Card 49           |  |  |  |

| Design of the Factory-Installed RAM Expansion Card |  |  |  |

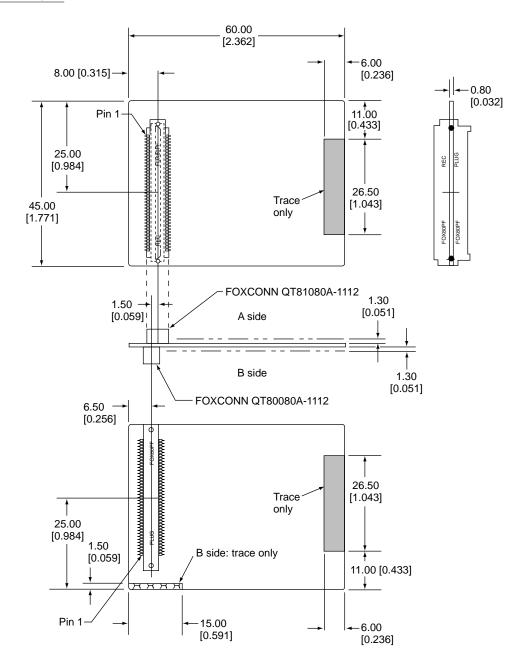

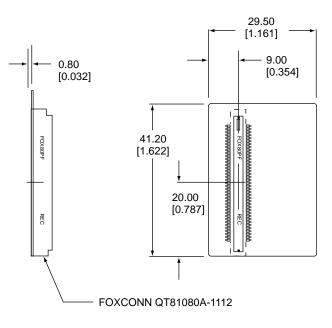

| RAM Card Connectors 52                             |  |  |  |

| Expansion Card and Connector 52                    |  |  |  |

| Expansion Card Connector 52                        |  |  |  |

| Signals on the Expansion Card Connector 52         |  |  |  |

| Expansion Card Mechanical Design 54                |  |  |  |

| PC Card Slot 57                                    |  |  |  |

| PC Card Features 58                                |  |  |  |

| Summary Specifications 58                          |  |  |  |

| Access Windows 58                                  |  |  |  |

| Data Access 59                                     |  |  |  |

| Signal Definitions 59                              |  |  |  |

| Power 59                                           |  |  |  |

| Controller Interrupts 60                           |  |  |  |

# Chapter 5 Software Features 61

| ROM Software 62                |    |

|--------------------------------|----|

| Machine Identification 62      |    |

| Larger Flat Panel Displays 62  |    |

| System Software 62             |    |

| Modified Software Components   | 63 |

| Apple Guide 63                 |    |

| Apple Menu Options 63          |    |

| CloseView 63                   |    |

| Enabler 63                     |    |

| File Sharing 64                |    |

| Finder 64                      |    |

| Find File 64                   |    |

| General Controls Control Panel | 64 |

| Memory Control Panel 64        |    |

| Monitors & Sound 65            |    |

| Native Resource Manager 65     |    |

| Open Transport 65              |    |

| SimpleText 65                  |    |

| Consolidation of Files 65      |    |

| Open Transport 66              |    |

| New Features of Open Transport | 67 |

| Compatibility 67               |    |

| 1 V                            |    |

Glossary 69

# Figures and Tables

| Chapter 1 | Introduction                                                                                                                                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Figure 1-1<br>Figure 1-2                                                                                                                                                                              | Front view of the computer4Rear view of the computer5                                                                                                                                                                                                                                                                                                                                                                                 |

|           | Table 1-1                                                                                                                                                                                             | Configurations 5                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Chapter 2 | Architecture                                                                                                                                                                                          | 7                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|           | Figure 2-1                                                                                                                                                                                            | Block diagram 9                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Chapter 3 | I/O Features                                                                                                                                                                                          | 15                                                                                                                                                                                                                                                                                                                                                                                                                                    |

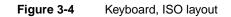

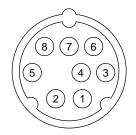

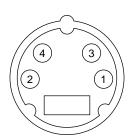

|           | Figure 3-1<br>Figure 3-2<br>Figure 3-3<br>Figure 3-4<br>Figure 3-5<br>Figure 3-6<br>Table 3-1<br>Table 3-2<br>Table 3-3<br>Table 3-4<br>Table 3-5<br>Table 3-6                                        | Maximum dimensions of the internal IDE hard disk17Connector for the internal IDE hard disk18Keyboard, U.S. layout21Keyboard, ISO layout21Serial port connector23ADB connector25Signal assignments on the IDE hard disk connector18Signals on the IDE hard disk connector19Characteristics of the displays22Serial port signals23SCSI connector pin assignments25                                                                      |

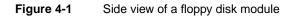

| Chapter 4 | Expansion Mo<br>Figure 4-1<br>Figure 4-2<br>Figure 4-3<br>Figure 4-3<br>Figure 4-5<br>Figure 4-5<br>Figure 4-6<br>Figure 4-7<br>Figure 4-8<br>Figure 4-9<br>Figure 4-10<br>Figure 4-11<br>Figure 4-12 | Side view of a floppy disk module30Top view of a floppy disk module31Bottom view of a floppy disk module32Top view of a CD-ROM module33Bottom view of a CD-ROM module34User-installed RAM expansion card50Factory-installed RAM card51Height limits on the connector side51Component side of the expansion card55Trace side of the expansion card55Height restrictions on the component side56Height restrictions on the trace side57 |

|           | Table 4-1<br>Table 4-2                                                                                                                                                                                | Connectors for expansion bay modules 34<br>Signal assignments on the floppy disk connector 35                                                                                                                                                                                                                                                                                                                                         |

| Table 4-3  | Signals on the floppy disk connector 35                        |

|------------|----------------------------------------------------------------|

| Table 4-4  | Signal assignments on the CD-ROM connector 36                  |

| Table 4-5  | Signal assignments for a hard disk drive 37                    |

| Table 4-6  | Signals on the CD-ROM connector 38                             |

| Table 4-7  | Unused IDE signals 39                                          |

| Table 4-8  | Signals on the RAM expansion connectors 41                     |

| Table 4-9  | Descriptions of signals on the RAM expansion connector 43      |

| Table 4-10 | Address multiplexing for some typical DRAM devices 45          |

| Table 4-11 | Configurations of RAM banks 46                                 |

| Table 4-12 | RAM bank selection 47                                          |

| Table 4-13 | Bank selection signal connections 47                           |

| Table 4-14 | Signals on the expansion card connector 52                     |

| Table 4-15 | Descriptions of the signals on the expansion card connector 54 |

# About This Developer Note

This developer note is a concise description of the Epic computer, with emphasis on the features that are new or different from those of earlier Macintosh PowerBook computers.

This developer note is intended to help hardware and software developers design products that are compatible with the Macintosh products described in the note. If you are not already familiar with Macintosh computers or if you would simply like more technical information, you may wish to read the supplementary reference documents described in this preface.

#### Important

This note contains preliminary information about forthcoming Apple products. The information in this note is subject to change; no representation or guarantee is made about its accuracy or completeness. ▲

This note is published in two forms: a paper version and an online version. The paper version is available through the *Apple Developer Catalog* (ADC). For information about ADC, see "Supplemental Reference Documents," later in this preface.

You can obtain the online version in two ways:

- on the Internet, under the heading Developer Notes at http://www.devworld.apple.com/dev/techsupport.shtml

- on the Reference Library Edition of the Developer CD Series, available through the Apple Developer Catalog.

# Contents of This Note

The information in this note is arranged in five chapters.

- Chapter 1, "Introduction," introduces the Epic computer and describes its new features.

- Chapter 2, "Architecture," describes the internal logic of the computer, including the main ICs that appear in the block diagram.

- Chapter 3, "I/O Features," describes the input/output features, including both the internal I/O devices and the external I/O ports.

- Chapter 4, "Expansion Modules," describes the expansion features of interest to developers. It includes development guides for expansion bay devices, the RAM expansion card, the expansion card, and the PC card slot.

Chapter 5, "Software Features," describes the new features of the ROM and system software, with the emphasis on software that is specific to this computer.

This developer note also contains a glossary and an index.

# Supplemental Reference Documents

The following documents provide information that complements or extends the information in this developer note.

### Apple Publications

To see how the Epic computer is similar to the Macintosh PowerBook 5300 computer, developers should have copies of *Macintosh Developer Note Number 14*. The developer note is available on the Developer CD series and through ADC.

For information about PC cards and the PCMCIA slot, developers should have a copy of *PC Card Expansion for PowerBook Computers*. Developers should also have copies of the appropriate Apple reference books, including the relevant volumes of *Inside Macintosh*. These Apple books are available in technical bookstores and through ADC.

The *Apple Developer Catalog* (ADC) is Apple Computer's worldwide source for hundreds of development tools, technical resources, training products, and information for anyone interested in developing applications on Apple computer platforms. Customers receive the *Apple Developer Catalog* featuring all current versions of Apple development tools and the most popular third-party development tools. ADC offers convenient payment and shipping options, including site licensing.

To order products or to request a complimentary copy of the *Apple Developer Catalog*, contact

Apple Developer Catalog Apple Computer, Inc. P.O. Box 319 Buffalo, NY 14207-0319

| Telephone | 1-800-282-2732 (United States)<br>1-800-637-0029 (Canada)<br>716-871-6555 (International) |

|-----------|-------------------------------------------------------------------------------------------|

| Fax       | 716-871-6511                                                                              |

| AppleLink | ORDER.ADC                                                                                 |

| Internet  | order.adc@applelink.apple.com                                                             |

### **Other Publications**

For information about programming the PowerPC<sup>™</sup> family of microprocessors, developers should have copies of Motorola's *PowerPC* 601 *RISC Microprocessor User's Manual* and *PowerPC* 603e *Microprocessor Implementation Definition Book IV*.

For information about ATA devices such as the built-in IDE hard disk, developers should have access to the following ANSI specifications:

- ATA/IDE specification, ANSI proposal X3T10/0948D, Revision 2K or later (ATA-2)

- ATAPI specification, ANSI proposal X3T13/1153D AT Attachment-4 with Packet Interface Extension, Revision 2 (ATA/ATAPI-4)

For information about the sound codec used in the custom sound IC, developers should refer to the IT&T ASCO 2300 Audio-Stereo Code Specification.

For information about PC cards and the PCMCIA slot, developers should refer to the *PCMCIA PC Card Standard*, Release 2.1. You can order that book from

Personal Computer Memory Card International Association 1030G East Duane Avenue Sunnyvale, CA 94086 Phone: 408-720-0107 Fax: 408-720-9416

# Conventions and Abbreviations

This developer note uses the following typographical conventions and abbreviations.

### Typographical Conventions

Computer-language text—any text that is literally the same as it appears in computer input or output—appears in Courier font.

Hexadecimal numbers are preceded by a dollar sign (\$). For example, the hexadecimal equivalent of decimal 16 is written as \$10.

#### Note

A note like this contains information that is of interest but is not essential for an understanding of the text.  $\blacklozenge$

#### IMPORTANT

A note like this contains important information that you should read before proceeding. ▲

#### Sidebar

Sidebars are used for information that is not part of the main discussion. A sidebar may contain information

about a related subject or technical details that are not required reading.

### WARNING

Warnings like this direct your attention to something that could cause injury to the user, damage to either hardware or software, or loss of data.  $\blacktriangle$

# **Standard Abbreviations**

Standard units of measure used in this note include

| А    | amperes             | MHz | megahertz                 |

|------|---------------------|-----|---------------------------|

| dB   | decibels            | mm  | millimeters               |

| GB   | gigabytes           | ms  | milliseconds              |

| Hz   | hertz               | mV  | millivolts                |

| Κ    | 1024                | μF  | microfarads               |

| KB   | kilobytes           | ns  | nanoseconds               |

| kbps | kilobits per second | Ω   | ohms                      |

| kHz  | kilohertz           | pF  | picofarads                |

| kΩ   | kilohms             | V   | volts                     |

| М    | 1,048,576           | VAC | volts alternating current |

| mA   | milliamperes        | VDC | volts direct current      |

| MB   | megabytes           | W   | watts                     |

Other abbreviations used in this note include

| \$ <i>n</i> | hexadecimal value <i>n</i>                      |

|-------------|-------------------------------------------------|

| AC          | alternating current                             |

| ADB         | Apple Desktop Bus                               |

| API         | application programming interface               |

| ASIC        | application-specific integrated circuit         |

| ATA         | AT attachment                                   |

| ATAPI       | ATA packet interface                            |

| AUI         | auxiliary unit interface                        |

| BCD         | binary coded decimal                            |

| CAS         | column address strobe (a memory control signal) |

| CCFL        | cold cathode fluorescent lamp                   |

| CD          | compact disc                                    |

| CD-ROM | compact-disc read-only memory                           |

|--------|---------------------------------------------------------|

| CIS    | card information structure                              |

| CLUT   | color lookup table                                      |

| CMOS   | complementary metal oxide semiconductor                 |

| CPU    | central processing unit                                 |

| CSC    | color screen controller                                 |

| DAA    | data access adapter (a telephone line interface)        |

| DAC    | digital-to-analog converter                             |

| DC     | direct current                                          |

| DCE    | device control entry (a data structure)                 |

| DDM    | driver descriptor map                                   |

| DOS    | Disk Operating System                                   |

| DRAM   | dynamic RAM                                             |

| DSP    | digital signal processor                                |

| FIFO   | first in, first out                                     |

| FPU    | floating-point unit                                     |

| FSTN   | film supertwist nematic (a type of LCD)                 |

| HBA    | host bus adapter                                        |

| IC     | integrated circuit                                      |

| IDE    | integrated device electronics                           |

| I/O    | input/output                                            |

| IR     | infrared                                                |

| LCD    | liquid crystal display                                  |

| LS TTL | low-power Schottky TTL (a standard type of device)      |

| MMU    | memory management unit                                  |

| NiCad  | nickel cadmium                                          |

| NiMH   | nickel metal hydride                                    |

| PCMCIA | Personal Computer Memory Card International Association |

| PDS    | processor-direct slot                                   |

| PROM   | programmable read-only memory                           |

| PWM    | pulse width modulation                                  |

| RAM    | random-access memory                                    |

| RAMDAC | random-access memory, digital-to-analog converter       |

| RAS    | row address strobe                                      |

| RGB    | red-green-blue (a type of color video system)           |

| RISC   | reduced instruction set computing                       |

| rms    | root mean square                                        |

| ROM    | read-only memory                                        |

|        |                                                         |

| SCC  | Serial Communications Controller                        |

|------|---------------------------------------------------------|

| SCSI | Small Computer System Interface                         |

| SNR  | signal-to-noise ratio                                   |

| SOJ  | small outline J-lead package                            |

| SOP  | small outline package                                   |

| SRAM | static RAM                                              |

| SVGA | super video graphics adapter                            |

| TDM  | time-division multiplexing                              |

| TFT  | thin-film transistor (a type of LCD)                    |

| TSOP | thin small outline package                              |

| TTL  | transistor-transistor logic (a standard type of device) |

| VCC  | positive supply voltage (voltage for collectors)        |

| VGA  | video graphics adapter                                  |

| VRAM | video RAM                                               |

#### CHAPTER 1

#### Introduction

The Epic computer is an all-in-one notebook computer based on the PowerBook 5300 computer but with improved capabilities and an all-new case design. The Epic computer has a PC card slot, an expansion bay, an internal expansion slot, an infrared link, and space for a rechargeable battery.

## Features

Many of the features of the Epic computer are similar to those of the Macintosh 5300 computer. The features that are different are listed first; all the features are described later in this developer note.

### **New Features**

Here is a list of the new features of the Epic computer.

- **Case design:** The Epic computer has a new case design. The display assembly includes a panel that the user can remove or replace to personalize the computer.

- CD-ROM drive: The computer can accommodate a 5.25-inch CD-ROM drive in its expansion bay. Some configurations include a Macintosh 6x-speed CD-ROM drive.

- Internal expansion: The computer has an internal slot that supports an expansion card.

### Modified Features

Here is a list of the features of the Epic computer that are different from the features of the Macintosh PowerBook 5300.

- **Processor**: The Epic computer has a PowerPC<sup>TM</sup> 603e microprocessor running at a clock frequency of 117 MHz.

- RAM: The computer comes with 12 or 16 MB of low-power, self-refreshing dynamic RAM (DRAM).

- **RAM expansion:** The computer can accept two RAM expansion cards with up to 24 MB each, for a total of up to 64 MB of RAM.

- Hard disk: The computer has one internal 2.5-inch IDE hard disk drive with a storage capacity of 750 MB or 1 GB.

- **Display:** The computer has a 11.3 inch color display with SVGA resolution (800 by 600 pixels). The display is backlit by a cold cathode fluorescent lamp (CCFL).

- Video output: The video output card is optional.

- Expansion bay: The computer has an opening that accepts a plug-in module with a 5.25-inch CD-ROM drive, a 1.4 MB DOS-compatible floppy disk drive, or some other IDE storage device. The expansion bay is larger than the one in the PowerBook 5300, but it can accept modules designed for that computer.

- **Networking:** The computer has a built-in LocalTalk network interface. An optional Ethernet card can be installed in the internal expansion slot or in a PC card slot.

- **Trackpad:** The integrated flat pad includes tap/double tap and drag. It is similar to the trackpad in the Macintosh PowerBook 190 computer.

- Weight: The computer weighs 6.5 pounds with the battery and a floppy disk drive installed.

- **Size:** The computer is 11 inches wide, 9 inches deep, and 2 inches high.

- Security connector: The computer has a Kensington Security Connector on the back panel that allows users to attach a security device.

### **Unchanged Features**

Here is a list of the features that are the same as those of the PowerBook 5300. For the sake of completeness, these features are described in the later chapters of this developer note.

- Disk mode: With an optional HDI-30 SCSI Disk Adapter cable, the computer allows the user to read and store data on the computer's internal hard disk from another Macintosh computer.

- Floppy disk: The computer comes with a 1.4 MB floppy disk drive in the expansion bay.

- **PC card slot:** The computer accepts one type III or two type II PC cards.

- Modem: The computer accepts a PC card modem.

- Standard I/O ports: The computer has all the standard Macintosh inputs and outputs. The I/O ports are an HDI-30 connector for external SCSI devices, a 4-pin mini-DIN Apple Desktop Bus (ADB) port, an 8-pin mini-DIN serial port, stereo audio input and output jacks, and a video output connector (video support is optional).

- **Sound:** The computer has a built-in microphone and speaker as well as a line-level input jack and a stereo headphone jack.

- Keyboard: The keyboard design provides 76 (United States) or 77 (ISO) keys, including 12 function keys.

- Infrared link: The computer has an infrared module that can communicate with other IR-equipped PowerBook computers at speeds up to 230 KB per second.

- Batteries: The computer has space for one Macintosh PowerBook Rechargeable Battery. The battery is an improved NiMH type with a capacity of 30 watt-hours. It can operate the computer for up to five hours.

- **Power supply:** The computer comes with an external recharger/power adapter that accepts any worldwide standard voltage from 100 to 240 volts AC at 50 to 60 Hz.

#### Note

The power adapter for the Epic looks a lot like the one for the PowerBook 5300, but it is not the same. Among other things, the connectors are different.

# Appearance

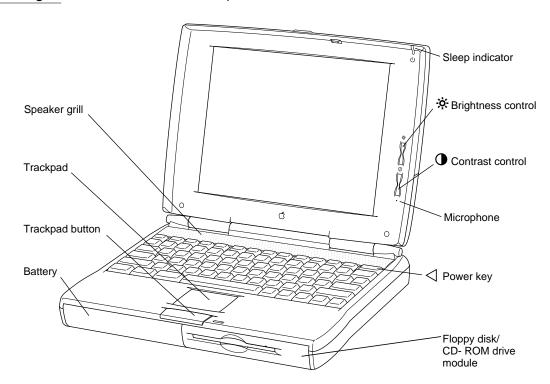

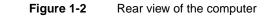

The Epic computer has an all-new streamlined case with more flexibility than earlier PowerBook models. Figure 1-1 shows a front view of the computer in the open position. Figure 1-2 shows a rear view of the computer.

Figure 1-1 Front view of the computer

# Configurations

The Epic computer is available in three configurations, as shown in Table 1-1.

| Table 1-     | 1 Config    | jurations         |                          |                     |                  |

|--------------|-------------|-------------------|--------------------------|---------------------|------------------|

| Model number | RAM<br>size | Hard<br>disk size | Display size<br>(pixels) | Display type        | CD-ROM<br>drive? |

| Epic cs      | 12 MB       | 750 MB            | 800 by 600               | DualScan color      | No               |

| Epic cs      | 16 MB       | 750 MB            | 800 by 600               | DualScan color      | Yes              |

| Epic c       | 16 MB       | 1 GB              | 800 by 600               | Active-matrix color | Yes              |

#### Note

The 12 MB configuration has 8 MB of RAM on the main logic board and an additional 4 MB on a factory-installed RAM expansion card. The 16 MB configuration has 8 MB on the factory-installed RAM expansion card. That card is in addition to the user-accessible RAM expansion cards. For more information, see "RAM Expansion Cards" beginning on page 40. ◆

# **Peripheral Devices**

In addition to the devices that are included with the computer, several peripheral devices are available separately:

- The Macintosh PowerBook 8 MB Memory Expansion Kit for the Epic computer expands the RAM to 20 or 24 MB.

- The optional video output card can be installed in the internal expansion slot. The card is similar to the one used in the Macintosh PowerBook 5300. The video card supports video monitors with up to 624 by 832 pixels at 8 bits per pixel.

- The Macintosh 6x-speed CD-ROM drive fits into the expansion bay.

- The Macintosh PowerBook Rechargeable Battery is available separately as an additional or replacement battery.

- The Macintosh PowerBook 45W AC Adapter, which comes with the computer, is also available separately. The adapter can recharge the internal battery in just four hours while the computer is running or two hours while the computer is shut down or in sleep mode.

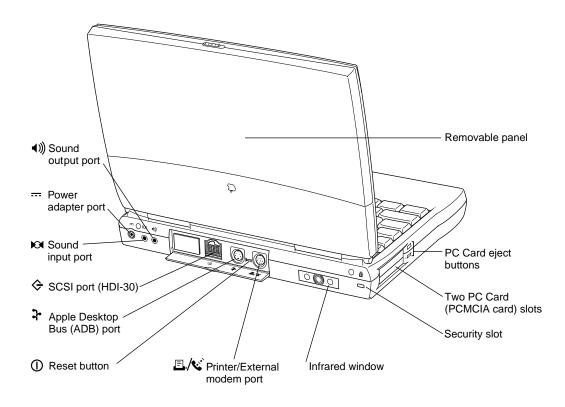

The architecture of the Epic computer is designed around two buses: the processor bus and the I/O bus. The processor and memory are connected to the processor bus, which operates at 33.33 MHz. The input and output devices are connected to the I/O bus, a 68030-compatible bus that operates at 25.175 MHz. An Apple custom IC called the PBX IC acts as the bridge between the two buses, translating processor bus cycles into single or multiple I/O bus cycles, as needed. The block diagram in Figure 2-1 shows the buses and the devices that are connected to them.

#### Note

Except for the floppy disk controller IC, the architecture of the Epic computer is similar to that of the Macintosh PowerBook 5300 computer. ◆

# Devices on the Processor Bus

The processor bus connects the PowerPC 603e microprocessor, the main RAM, and the ROM. Optional RAM expansion cards can be plugged into the logic board and are also connected to the processor bus.

### Main Processor

The main processor in the Epic computer is a PowerPC 603e microprocessor, an enhanced version of the PowerPC 603. Its principal features include

- full RISC processing architecture

- a load-store unit that operates in parallel with the processing units

- a branch manager that can usually implement branches by reloading the incoming instruction queue without using any processing time

- two internal memory management units (MMUs), one for instructions and one for data

- two 16 KB on-chip caches for data and instructions

For technical details, please refer to the reference books listed in the preface.

The PowerPC 603e microprocessor in the Epic computer runs at a clock speed of 116.67 MHz. The microprocessor's clock speed is locked at 3.5 times the processor bus's clock speed, which is 33.33 MHz.

#### Figure 2-1 Block diagram

### RAM

The Epic computer has 8 MB of dynamic RAM (DRAM) soldered on the main logic board. The computer comes with a factory-installed internal RAM expansion card that adds another 4 or 8 MB of RAM for a total of 12 or 16 MB of RAM. The RAM ICs are low-power, self-refreshing type with an access time of 70 ns.

In addition to the factory-installed RAM expansion card, one or two optional RAM expansion cards can be installed by way of an 80-pin connector on the logic board. With the full complement of RAM expansion cards, the computer supports up to 64 MB of RAM. See the section "RAM Expansion Cards" beginning on page 40 for details.

Memory control is provided by the PBX custom IC, which has a memory bank decoder in the form of an indexed register file. By writing the appropriate values into the register file at startup time, the system software makes the memory addresses contiguous from \$0000 0000 even if some banks are not populated. See "PBX Memory Controller IC" on page 10.

## ROM

The ROM in the Epic computer is implemented as a 1 M by 32-bit array consisting of two 1 M by 16-bit ROM ICs. The ROM devices support burst mode, so they do not degrade the performance of the PowerPC 603e microprocessor. The ROM ICs provide 4 MB of storage, which is located in the system memory map between addresses \$3000 0000 and \$3FFF FFFF. The ROM data path is 32 bits wide and addressable only as longwords. See Chapter 5, "Software Features," for a description of the features of this new ROM.

# **PBX Memory Controller IC**

The PBX IC is an Apple custom IC that provides RAM and ROM memory control and also acts as the bridge between the processor bus and the 68030-type I/O bus. The PBX IC also provides bus cycle decoding for the floppy disk controller.

### Memory Control

The PBX IC controls the system RAM and ROM and provides address multiplexing and refresh signals for the DRAM devices. For information about the address multiplexing, see "Address Multiplexing" beginning on page 44.

The PBX IC has a memory bank decoder in the form of an indexed register file. Each nibble in the register file represents a 2 MB page in the memory address space (64 MB). The value in each nibble maps the corresponding page to one of the eight banks of physical RAM. By writing the appropriate values into the register file at startup time, the system software makes the memory addresses contiguous.

#### **Bus Bridge**

The PBX IC acts as a bridge between the processor bus and the I/O bus, converting signals on one bus to the equivalent signals on the other bus. The bridge functions are performed by two converters. One accepts requests from the processor bus and presents them to the I/O bus in a manner consistent with a 68030 microprocessor. The other converter accepts requests from the I/O bus and provides access to the RAM and ROM on the processor bus.

The bus bridge in the PBX IC runs asynchronously so that the processor bus and the I/O bus can operate at different rates. The processor bus operates at a clock rate of 33.33 MHz, and the I/O bus operates at 25.175 MHz.

# Devices on the I/O Bus

The following components communicate by way of the I/O bus:

- the Whitney custom IC

- the Combo I/O controller IC

#### CHAPTER 2

#### Architecture

- the Singer sound controller IC

- the Power Manager IC

- the display controller IC (ECSC)

- the video card connector

- the Baboon custom IC, which controls the expansion bay

- the 82078 IC , which controls a floppy disk drive in the expansion bay

- the TREX custom IC , which controls the PC card slots

The next sections describe these components.

## Whitney Peripheral Support IC

The Whitney IC is a custom IC that provides the interface between the system bus and the I/O bus that supports peripheral device controllers. The Whitney IC incorporates the following circuitry:

- VIA1 like that in other Macintosh computers

- SWIM II floppy disk controller

- CPU ID register

The Whitney IC also performs the following functions:

- bus error timing for the I/O bus

- bus arbitration for the I/O bus

- interrupt prioritization

- VIA2 functions

- sound data buffering

- clock generation

- power control signals

The Whitney IC contains the interface circuitry for the following peripheral ICs:

- Combo, which is a combination of SCC and SCSI ICs

- Singer, the sound codec IC

The Whitney IC provides the device select signals for the following ICs:

- the flat panel display controller

- the external video controller

The Whitney IC also provides the power off and reset signals to the peripheral device ICs.

# Combo IC

The Combo custom IC combines the functions of the SCC IC (85C30 Serial Communications Controller) and the SCSI controller IC (53C80). The SCC portion of the Combo IC supports the serial I/O port. The SCSI controller portion of the Combo IC supports the external SCSI devices.

# Singer IC

The Singer custom IC is a 16-bit digital sound codec. It conforms to the IT&T *ASCO 2300 Audio-Stereo Code Specification*. The Whitney IC maintains sound I/O buffers in main memory for sound samples being sent in or out through the Singer IC. For information about the operation of the Singer IC, see "Sound System" beginning on page 26.

# Power Manager IC

The Power Manager IC is a 68HC05 microprocessor that operates with its own RAM and ROM. The Power Manager IC performs the following functions:

- controlling sleep, shutdown, and on/off modes

- controlling power to the other ICs

- controlling clock signals to the other ICs

- supporting the ADB

- scanning the keyboard

- controlling display brightness

- monitoring battery charge level

- controlling battery charging

# **Display Controller IC**

An ECSC (enhanced color support chip) IC provides the data and control interface to the LCD panel. The ECSC IC contains a 256-entry CLUT, RAMDAC, display buffer controller, and flat panel control circuitry. For more information, see "Flat Panel Display Circuitry" on page 22.

# Video Card Connector

The Epic computer accepts an optional video ouput card that drives an external video monitor. For more information, see "Expansion Card and Connector" beginning on page 52.

# Baboon Custom IC

The Baboon custom IC provides the interface to the expansion bay. The IC performs four functions:

- controls the expansion bay

- controls the IDE interfaces, both internal and in the expansion bay

- buffers the floppy disk signals to the expansion bay

- decodes addresses for the PC card slots and the IDE controller

The Baboon IC controls the power to the expansion bay and the signals that allow the user to insert a device into the expansion bay while the computer is operating. Those signals are fully described in "Expansion Bay" beginning on page 30.

The Baboon IC controls the interface for both the internal IDE hard disk drive and a possible second IDE drive in the expansion bay. For information about the internal IDE drive see the section "Internal IDE Hard Disk Drive" beginning on page 16. For information about the IDE drive signals in the expansion bay, see "Signals on the Floppy Disk Connector" beginning on page 34, particularly Table 4-3 on page 35.

The Baboon IC also handles the signals to a floppy disk drive installed in the expansion bay. For more information, see "Signals on the Floppy Disk Connector," particularly Table 4-3 on page 35.

The address decode portion of the Baboon IC provides address decoding for the IDE controller portion of the IC. It also provides the chip select decode for the TREX custom IC and address decoding for the two PC card slots.

# Floppy Disk Controller IC

The floppy disk drive for the Epic computer is a 1.4 MB drive identical to those in previous PowerBook computers. The floppy disk controller is a standard 82078 IC.

The floppy disk drive for the Epic computer has a special signal, DISK\_IN\_PLACE, that indicates to the driver software whether a disk is present in the drive. For more information about the signal interface for devices in the expansion bay, see "Expansion Bay Connectors" beginning on page 34.

# TREX Custom IC

The TREX custom IC provides the interface and control signals for the PC card slots. The main features of the TREX IC are

- the interrupt structure for the PC card slots

- transfers of single-byte and word data to and from the PC card slots

- power management for the PC card slots, including

- $\Box$  sleep mode

- □ control of power to individual sockets

- □ support of insertion and removal of PC cards while the computer is operating

- support for software control of card ejection

- support for time-division multiplexing (TDM), Apple Computer's technique for implementing PC cards for telecommunications

For more information about the operation of the PC card slots, see "PC Card Slot" beginning on page 57.

14

# I/O Features

Seed Draft. Preliminary, Confidential. ©1996 Apple Computer, Inc. 8/26/96

CHAPTER 3

#### I/O Features

This chapter describes the input/output features of the Epic computer, including the built-in I/O devices and the ports for external I/O devices.

This chapter describes the following built-in devices and I/O ports:

- internal IDE hard disk drive

- built-in trackpad

- built-in keyboard

- built-in flat panel display

- serial port

- SCSI port

- Apple Desktop Bus (ADB) port

- IR module

- sound system

# Internal IDE Hard Disk Drive

The Epic computer has an internal hard disk that uses the standard IDE (integrated drive electronics) interface. This interface, used for IDE drives on IBM AT–compatible computers, is also referred to as the ATA interface. The implementation of the ATA interface on the Epic computer is a subset of the ATA/IDE specification, ANSI proposal X3T10/0948D, Revision 2K (ATA-2).

The software that supports the internal hard disk is the same as that in previous Macintosh PowerBook models with internal IDE drives. For a complete description of the software, see "Software for ATA Devices" in *Macintosh Developer Note Number 14*.

### Hard Disk Specifications

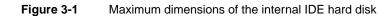

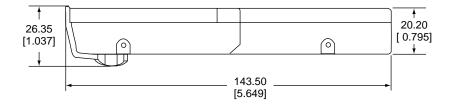

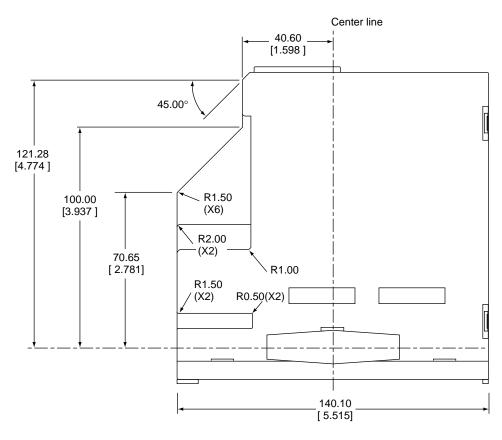

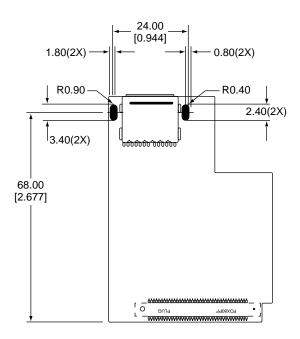

Figure 3-1 shows the maximum dimensions of the hard disk and the locations of the mounting holes. The minimum clearance between any conductive components on the drive and the bottom of the mounting envelope is 0.5 mm.

I/O Features

Note: Dimensions are in millimeters [inches]

### Hard Disk Connector

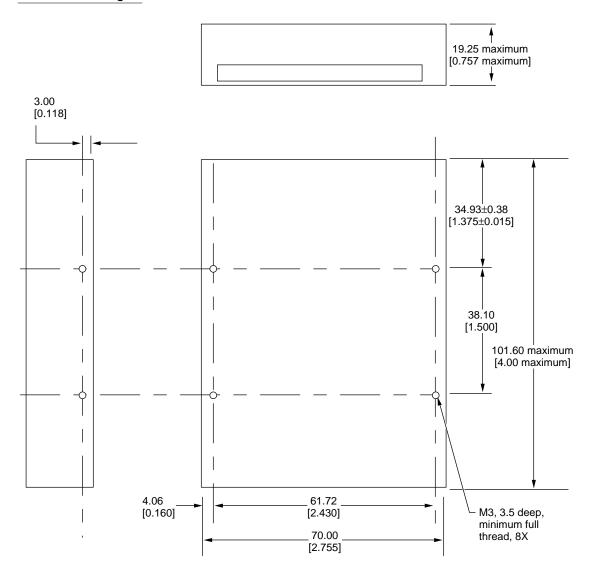

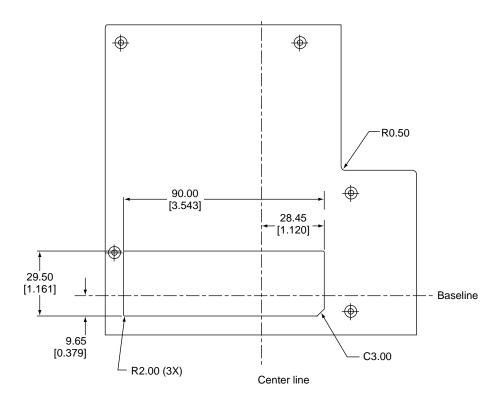

The internal hard disk has a 48-pin connector that carries both the IDE signals and the power for the drive. The connector has the dimensions of a 50-pin connector, but with one row of pins removed, as shown in Figure 3-2. The remaining pins are in two groups: pins 1–44, which carry the signals and power, and pins 46–48, which are reserved. Notice that pin 20 has been removed, and that pin 1 is located nearest the gap, rather than at the end of the connector.

CHAPTER 3

I/O Features

#### Figure 3-2 Connector for the internal IDE hard disk

Note: Dimensions are in millimeters [inches]

### **Signal Assignments**

Table 3-1 shows the signal assignments on the 44-pin portion of the hard disk connector. A slash (/) at the beginning of a signal name indicates an active-low signal.

| Pin<br>number | Signal name | Pin<br>number | Signal name |

|---------------|-------------|---------------|-------------|

| 1             | /RESET      | 2             | GROUND      |

| 3             | DD7         | 4             | DD8         |

| 5             | DD6         | 6             | DD9         |

| 7             | DD5         | 8             | DD10        |

| 9             | DD4         | 10            | DD11        |

| 11            | DD3         | 12            | DD12        |

| 13            | DD2         | 14            | DD13        |

| 15            | DD1         | 16            | DD14        |

| 17            | DD0         | 18            | DD15        |

| 19            | GROUND      | 20            | KEY         |

| 21            | DMARQ       | 22            | GROUND      |

| 23            | /DIOW       | 24            | GROUND      |

| 25            | /DIOR       | 26            | GROUND      |

| 27            | IORDY       | 28            | CSEL        |

| 29            | /DMACK      | 30            | GROUND      |

#### Table 3-1 Signal assignments on the IDE hard disk connector

continued

#### I/O Features

| Table 3-1     | Signal assignments on the IDI | E hard disk co | nnector (continued) |

|---------------|-------------------------------|----------------|---------------------|

| Pin<br>number | Signal name                   | Pin<br>number  | Signal name         |

| 31            | INTRQ                         | 32             | /IOCS16             |

| 33            | DA1                           | 34             | /PDIAG              |

| 35            | DA0                           | 36             | DA2                 |

| 37            | /CS0                          | 38             | /CS1                |

| 39            | /DASP                         | 40             | GROUND              |

| 41            | +5V LOGIC                     | 42             | +5V MOTOR           |

| 43            | GROUND                        | 44             | Reserved            |

# **IDE Signal Descriptions**

Table 3-2 describes the signals on the IDE hard disk connector.

| Signal name | Signal description                                                                                                                                                                                                                                                   |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| /CS0        | IDE register select signal. It is asserted low to select the main task file registers. The task file registers indicate the command, the sector address, and the sector count.                                                                                       |

| /CS1        | IDE register select signal. It is asserted low to select the additional control and status registers on the IDE drive.                                                                                                                                               |

| CSEL        | Cable select; if CSEL is asserted, the device address is 1; if negated, the device address is 0.                                                                                                                                                                     |

| DA(0-2)     | IDE device address; used by the computer to select one of the registers in the IDE drive. For more information, see the descriptions of the /CS0 and /CS1 signals.                                                                                                   |

| /DASP       | Device active or slave present.                                                                                                                                                                                                                                      |

| DD(0–15)    | IDE data bus; buffered from IOD(16–31) of the computer's I/O bus. DD(0–15) are used to transfer 16-bit data to and from the drive buffer. DD(8–15) are used to transfer data to and from the internal registers of the drive, with DD(0–7) driven high when writing. |

| /DIOR       | IDE I/O data read strobe.                                                                                                                                                                                                                                            |

| /DIOW       | IDE I/O data write strobe.                                                                                                                                                                                                                                           |

| /DMACK      | Used by the host to initiate a DMA transfer in response to DMARQ.                                                                                                                                                                                                    |

| DMARQ       | Asserted by the device when it is ready to transfer data to or from the host.                                                                                                                                                                                        |

continued

CHAPTER 3

I/O Features

| Table 3-2   | Signals on the IDE hard disk connector (continued)                                                                                                |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal name | Signal description                                                                                                                                |

| INTRQ       | IDE interrupt request. This active-high signal is used to inform the computer that a data transfer is requested or that a command has terminated. |

| /IOCS16     | IDE I/O channel select; asserted low for an access to the data port. The computer uses this signal to indicate a 16-bit data transfer.            |

| IORDY       | IDE I/O ready; when driven low by the drive, signals the CPU to insert wait states into the I/O read or write cycles.                             |

| KEY         | This pin is the key for the connector.                                                                                                            |

| /PDIAG      | Asserted by device 1 to indicate to device 0 that it has completed the power-on diagnostics.                                                      |

| /RESET      | Hardware reset to the drive; an active-low signal.                                                                                                |

|             |                                                                                                                                                   |

The IDE data bus is connected to the I/O bus through bidirectional bus buffers. To match the big-endian format of the 68030-compatible I/O bus, the bytes are swapped. The lowest byte of the IDE data bus, DD(0–7), is connected to the high byte of the upper word of the I/O bus, IOD(24–31). The highest byte of the IDE data bus, DD(8–15), is connected to the low byte of the upper word of the I/O bus, IOD(16–23).

# Trackpad

The pointing device in the Epic computer is a trackpad, an integrated flat pad that replaces the trackball used in previous PowerBook computers. The trackpad provides precise cursor positioning in response to motions of the user's fingertip over the surface of the pad. A single button below the trackpad is used to make selections.

The trackpad is a solid-state device that emulates a mouse by sensing the motions of the user's finger over its surface and translating those motions into ADB commands. The trackpad is lighter and more durable than the trackball used in earlier PowerBook computers, and it consumes less power.

The trackpad includes tap and double-tap features. As decribed in the user's manual, the trackpad responds to one or two taps on the pad itself as one or two clicks of the button. The user can tap and drag on the trackpad in much the same manner as clicking and dragging with the mouse.

# Keyboard

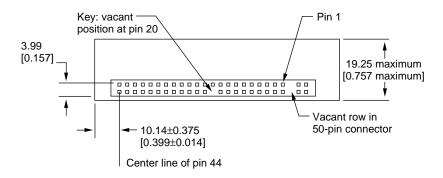

The keyboard provides 76 (United States) or 77 (ISO) keys, including 12 function keys. Figure 3-3 shows the version of the keyboard used on machines sold in the United States.

#### Trackpad

CHAPTER 3

I/O Features

Figure 3-4 shows the version of the keyboard used on machines sold in countries that require the ISO standard.

| esc F1 F2          | F3 F4 F5 F6                                                                | F7 F8 F9       | F10 F11 F12 0                     |

|--------------------|----------------------------------------------------------------------------|----------------|-----------------------------------|

| ± ! @ 2            | #         \$         %         ^           3         4         5         6 | & * (<br>7 8 9 |                                   |

| Q W                | ERTY                                                                       | UIO            | <pre></pre>                       |

| Ê A S              | 5 D F G                                                                    | H J K L        |                                   |

| ₫ <sup>~</sup> . Z | ХСУВ                                                                       | N M ,          | >         ?           .         / |

| ctrl 🖵             | <b>*</b> #                                                                 |                |                                   |

The Caps Lock key does not latch down. To indicate whether the caps lock is engaged, a software extension displays an icon in the menu bar.

The user can remove the keyboard to obtain access to the internal components and expansion connectors inside the computer. The keyboard is held in place by the perforated speaker grille. After sliding the grille to the left and lifting it out, the user can lift out the keyboard, which remains connected by a flexible ribbon cable.

I/O Features

#### Types of Displays

Flat panel displays come in two types: active-matrix and passive matrix.

Active-matrix displays, also called thin-film transistor (TFT) displays, have a driving transistor for each individual pixel. The driving transistors give active-matrix displays high contrast and fast response time. Passive matrix refers to a display technology that does not have individual transistors. That technology is also called FSTN, for film supertwist nematic, sometimes shortened to just supertwist. DualScan is Apple Computer's improved type of FSTN color display.

# Flat Panel Display

The Epic computer has a built-in flat panel display. Two display options are available, as shown in Table 3-3. Both displays are backlit by a cold cathode fluorescent lamp (CCFL). Both displays can show up to thousands of colors (16 bits per pixel).

| Table 3-3 | Characteristics of the displays |

|-----------|---------------------------------|

|-----------|---------------------------------|

| Display type                           | Size<br>(pixels) | Dot pitch<br>(mm) | Number of<br>colors or grays |

|----------------------------------------|------------------|-------------------|------------------------------|

| 11.3-inch DualScan<br>color (FSTN)     | 800 by 600       | 0.27              | Thousands                    |

| 11.3-inch active-matrix<br>color (TFT) | 800 by 600       | 0.27              | Thousands                    |

## Flat Panel Display Circuitry

The flat panel display circuitry in the Epic computer emulates a NuBus<sup>™</sup> video card installed in slot \$0. There is no declaration ROM as such; its functions have been incorporated into the system ROM. The display circuitry includes the new ECSC controller IC and a display buffer consisting of 1 MB of VRAM. The LCD display is compatible with software that uses QuickDraw and the Palette Manager. The display supports color-table animation.

## Number of Colors

The display controller IC contains a 256-entry CLUT. Although the CLUT supports a palette of thousands of colors, many of the possible colors do not look acceptable on the display. Due to the nature of color LCD technology, some colors are dithered or exhibit noticeable flicker. Apple has developed new gamma tables for these displays that minimize flicker and optimize available colors. With these gamma tables, the effective

range of the CLUT for the active-matrix color display is about 260,000 colors; for the DualScan color display, the effective range is about 4000 colors.

## Serial Port

The Epic computer has a standard Macintosh serial port for synchronous, asynchronous, or AppleTalk serial communication. The 8-pin mini-DIN connector on the back panel is the same as those on other Macintosh computers. Figure 3-5 shows the connector, and Table 3-4 shows the signal assignments for the serial port.

Figure 3-5

Serial port connector

| Table 3-4 | Serial port signals |

|-----------|---------------------|

|           | Ochai port Signais  |

| Pin number | Signal name | Signal description    |

|------------|-------------|-----------------------|

| 1          | HSKo        | Handshake output      |

| 2          | HSKi        | Handshake input       |

| 3          | TxD-        | Transmit data –       |

| 4          | SG          | Signal ground         |

| 5          | RxD-        | Receive data –        |

| 6          | TxD+        | Transmit data +       |

| 7          | GPi         | General-purpose input |

| 8          | RxD+        | Receive data +        |

|            |             |                       |

## SCSI Port

The SCSI port on the Epic computer supports the SCSI interface as defined by the American National Standards Institute (ANSI) X3T9.2 committee.

The external HDI-30 connector is identical to those used in other PowerBook models. The SCSI portion of the Combo IC connects directly to the external SCSI connector and can sink up to 48 mA through each of the pins connected to the SCSI bus. The data and control signals on the SCSI bus are active-low signals that are driven by open drain outputs.

Table 3-5 shows the signal assignments for the external SCSI connector. Note that pin 1 of the external SCSI connector is the /SCSI.DISK.MODE signal.

|            | 0                                           |            |             |

|------------|---------------------------------------------|------------|-------------|

| Pin number | Signal name                                 | Pin number | Signal name |

| 1          | /SCSI.DISK.MODE                             | 16         | /DB6        |

| 2          | /DB0                                        | 17         | GND         |

| 3          | GND                                         | 18         | / DB7       |

| 4          | /DB1                                        | 19         | /DBP        |

| 5          | TERMPWR (not used; reserved for future use) | 20         | GND         |

| 6          | /DB2                                        | 21         | / REQ       |

| 7          | /DB3                                        | 22         | GND         |

| 8          | GND                                         | 23         | /BSY        |

| 9          | / ACK                                       | 24         | GND         |

| 10         | GND                                         | 25         | /ATN        |

| 11         | /DB4                                        | 26         | /C/D        |

| 12         | GND                                         | 27         | /RST        |

| 13         | GND                                         | 28         | /MSG        |

| 14         | /DB5                                        | 29         | /SEL        |

| 15         | GND                                         | 30         | /I/O        |

|            |                                             |            |             |

| Table 3-5 | SCSI connector signals |

|-----------|------------------------|

|-----------|------------------------|

## ADB Port

The Apple Desktop Bus (ADB) port on the Epic computer is functionally the same as on other Macintosh computers.

The ADB connector is a 4-pin mini-DIN connector. Figure 3-6 shows the arrangement of the pins on the ADB connector.

The ADB is a single-master, multiple-slave serial communications bus that uses an asynchronous protocol and connects keyboards, graphics tablets, mouse devices, and other devices to the computer. The custom ADB microcontroller drives the bus and reads status from the selected external device. A 4-pin mini-DIN connector connects the ADB controller to the outside world. Table 3-6 lists the ADB connector pin assignments. For more information about the ADB, see *Guide to the Macintosh Family Hardware*, second edition.

#### Table 3-6 ADB connector pin assignments

| Pin number | Name | Description                                                                                                                                                |

|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | ADB  | Bidirectional data bus used for input and output; an<br>open collector signal pulled up to +5 volts through a<br>470-ohm resistor on the main logic board. |

| 2          | PSW  | Power on signal; generates reset and interrupt key combinations.                                                                                           |

| 3          | +5V  | +5 volts from the computer.                                                                                                                                |

| 4          | GND  | Ground from the computer.                                                                                                                                  |

#### IMPORTANT

The total current available for all devices connected to the +5V pins on the ADB is 100 mA.  $\blacktriangle$

## Infrared Link

The computer has an infrared (IR) link connected internally to serial port B. The IR link can communicate with other PowerBook computers that have IR links. When the computer is placed within a few feet of another machine with an IR link, it can send and receive serial data at up to 230 KB per second.

For LocalTalk operation, the IR module takes serial bits from the SCC and transmits them using a modified form of pulse encoding called PPM-4. This method of encoding uses four cycles of a 3.92 MHz carrier for each pulse, which increases the system's immunity to interference from fluorescent lights.

## Sound System

The 16-bit stereo audio circuitry provides high-quality sound input and output through the built-in microphone and speaker. The user can also connect external input and output devices by way of the sound input and output jacks.

The sound system is based on the Singer codec IC along with input and output amplifiers and signal conditioners. In the Epic computer, the Singer codec supports two channels of digital sound with sample sizes up to 16 bits and sample rates of 11.025 kHz, 22.05 kHz, and 44.1 kHz.

The frequency response of the sound circuits, not including the microphone and speaker, is within plus or minus 2 dB from 20 Hz to 20 kHz. Total harmonic distortion and noise is less than 0.05 percent with a 1V rms sine wave input. The signal-to-noise ratio (SNR) is 85 dB, with no audible discrete tones.

#### Note

All sound level specifications in this section are rms values. •

## Sound Inputs

The sound system accepts inputs from several sources:

- built-in microphone

- external sound input jack

- sound from the expansion bay

- 1-bit sound from the PC card slot

The sound signal from the built-in microphone goes through a dedicated preamplifier that raises its nominal 30 mV level to the 1 V level of the codec circuits in the Singer IC.

Stereo sound signals from the external sound input jack go through an analog multiplexer that selects either the external signals or the sound signals from the expansion bay. The multiplexer also lowers the levels of the maximum 2 V signal at the input jack to match the 1 V level of the codec circuits in the Singer IC.

The sound input jack has the following electrical characteristics:

- input impedance:  $6.8k\Omega$

- maximum level: 2.0 V rms

#### Note

The sound input jack accepts the maximum sound output of an audio CD without clipping. When working with sound sources that have significantly lower levels, you may wish to increase the sound output level. You can do that using the Sound Manager as described in *Inside Macintosh: Sound.* ◆

Stereo sound signals from the expansion bay go through an analog multiplexer that selects either those signals or the line signals from the external input jack. The multiplexer also raises the nominal 0.5 V level of the expansion bay sound to the 1 V input level of the codec circuits.

The sound input from the expansion bay has the following electrical characteristics:

- input impedance:  $3.2k\Omega$

- maximum level: 0.5 V rms

Each PC card has one sound output pin (SPKR\_OUT), and the computer accepts either one or two cards. The 1-bit digital signals from the sound output pins are exclusive-ORed together and routed to the built-in speaker and the external sound output jack.

## Sound Outputs

The sound system sends computer-generated sounds or sounds from an expansion bay device or PC card to a built-in speaker and to an external sound output jack. The sound output jack is located on the back of the computer.

The sound output jack provides enough current to drive a pair of low-impedance headphones. The sound output jack has the following electrical characteristics:

- output impedance: 33  $\Omega$

- minimum recommended load impedance: 32  $\Omega$

- maximum level: 1 V rms

- maximum current: 32 mA peak

The computer turns off the sound signals to the internal speaker when an external device is connected to the sound output jack and during power cycling.

I/O Features

**Expansion Modules**

This chapter describes the following expansion features of the Epic computer:

- expansion bay

- RAM expansion cards

- expansion card connector

- PC card slot

## **Expansion Bay**

The expansion bay is an opening in the Epic computer that accepts a plug-in disk drive such as a floppy disk or CD-ROM drive.

## Expansion Bay Module for Floppy Disk

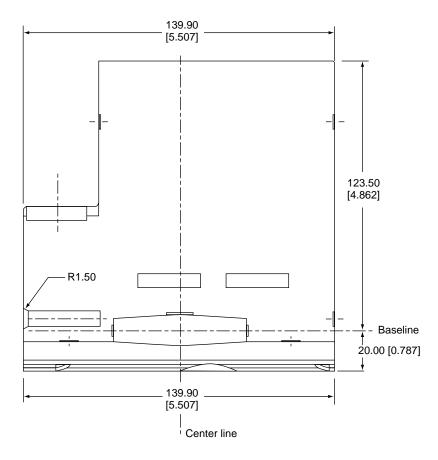

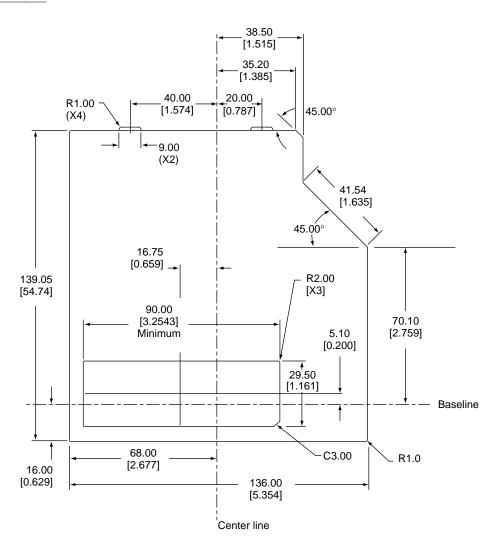

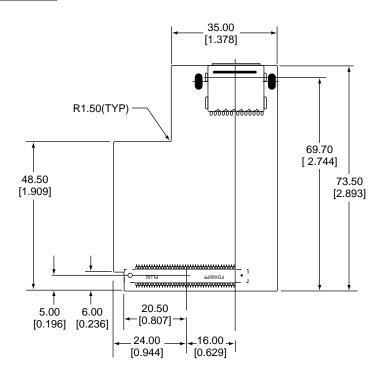

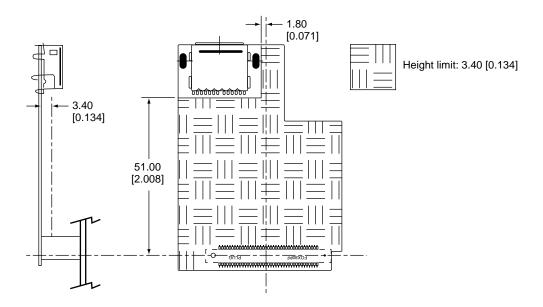

Figure 4-1 shows a side view of a floppy-disk module designed to fit into the expansion bay. Figure 4-2 shows a top view of such a module and Figure 4-3 shows a bottom view.

Note: Dimensions are in millimeters [inches]

#### Figure 4-2 Top view of a floppy disk module

Note: Dimensions are in millimeters [inches].

**Expansion Modules**

Bottom view of a floppy disk module

Note: Dimensions are in millimeters [inches].

32

## Expansion Bay Module for CD-ROM

Figure 4-4 shows a top view of a CD-ROM module designed to fit into the expansion bay. Figure 4-5 shows a bottom view of such a module.

#### Note

An expansion bay module for an IDE hard disk drive would be the same dimensions and use the same connector as a module for a CD-ROM drive. •

#### Figure 4-4

Top view of a CD-ROM module

Note: Dimensions are in millimeters [inches].

**Expansion Modules**

#### Figure 4-5 Bottom view of a CD-ROM module

Note: Dimensions are in millimeters [inches].

## **Expansion Bay Connectors**

The expansion bay has separate connectors for a floppy disk module and a CD-ROM or hard disk module. Table 4-1 shows the part numbers for connectors manufactured by KEL Connectors, Incorporated.

| Table 4-1 | Connectors | for expansion | bay modules |

|-----------|------------|---------------|-------------|

|-----------|------------|---------------|-------------|

| Type of module      | Connector in computer | Connector on module |

|---------------------|-----------------------|---------------------|

| Floppy-disk         | 89BF-020R             | 89BM-020R           |

| CD-ROM or hard disk | 8901-040-177L         | 8913-040-178MS-A    |

### Signals on the Floppy Disk Connector

Table 4-2 shows the signal assignments on the floppy disk connector. Signal names that begin with a slash (/) are active low.

| Pin | Signal name | Pin | Signal name |  |

|-----|-------------|-----|-------------|--|

| 1   | MB_+5V      | 2   | WRDATA      |  |

| 3   | MB_+5V      | 4   | DEV_ID(2)   |  |

| 5   | /FL_ENABLE  | 6   | GND         |  |

| 7   | GND         | 8   | HDSEL       |  |

| 9   | DEV_ID(1)   | 10  | GND         |  |

| 11  | /DEV_IN     | 12  | GND         |  |

| 13  | DEV_ID(0)   | 14  | /WRREQ      |  |

| 15  | GND         | 16  | PHASE(3)    |  |

| 17  | FD_RDATA    | 18  | PHASE(2)    |  |

| 19  | PHASE(0)    | 20  | PHASE(1)    |  |

|     |             |     |             |  |

Table 4-3 describes the signals on the floppy disk connector.

#### Table 4-3 Signals on the floppy disk connector

| Signal name | Signal description                                                                                                                                               |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DEV_ID(2–0) | These three signal lines identify the type of expansion-bay device.<br>A value of 000b identifies a floppy-disk drive; 011b identifies all<br>other IDE devices. |

| /DEV_IN     | This signal is low whenever a device is installed in the expansion bay; it is used by the Baboon IC to determine when a device has been inserted or removed.     |

| FD_RDATA    | Read data from the floppy disk drive.                                                                                                                            |

| /FL_ENABLE  | Floppy disk drive enable.                                                                                                                                        |

| GND         | Ground.                                                                                                                                                          |

| HDSEL       | Head select.                                                                                                                                                     |